Blog

Digital Logic Design MSc IT 1st Term Past paper 2017 UOS

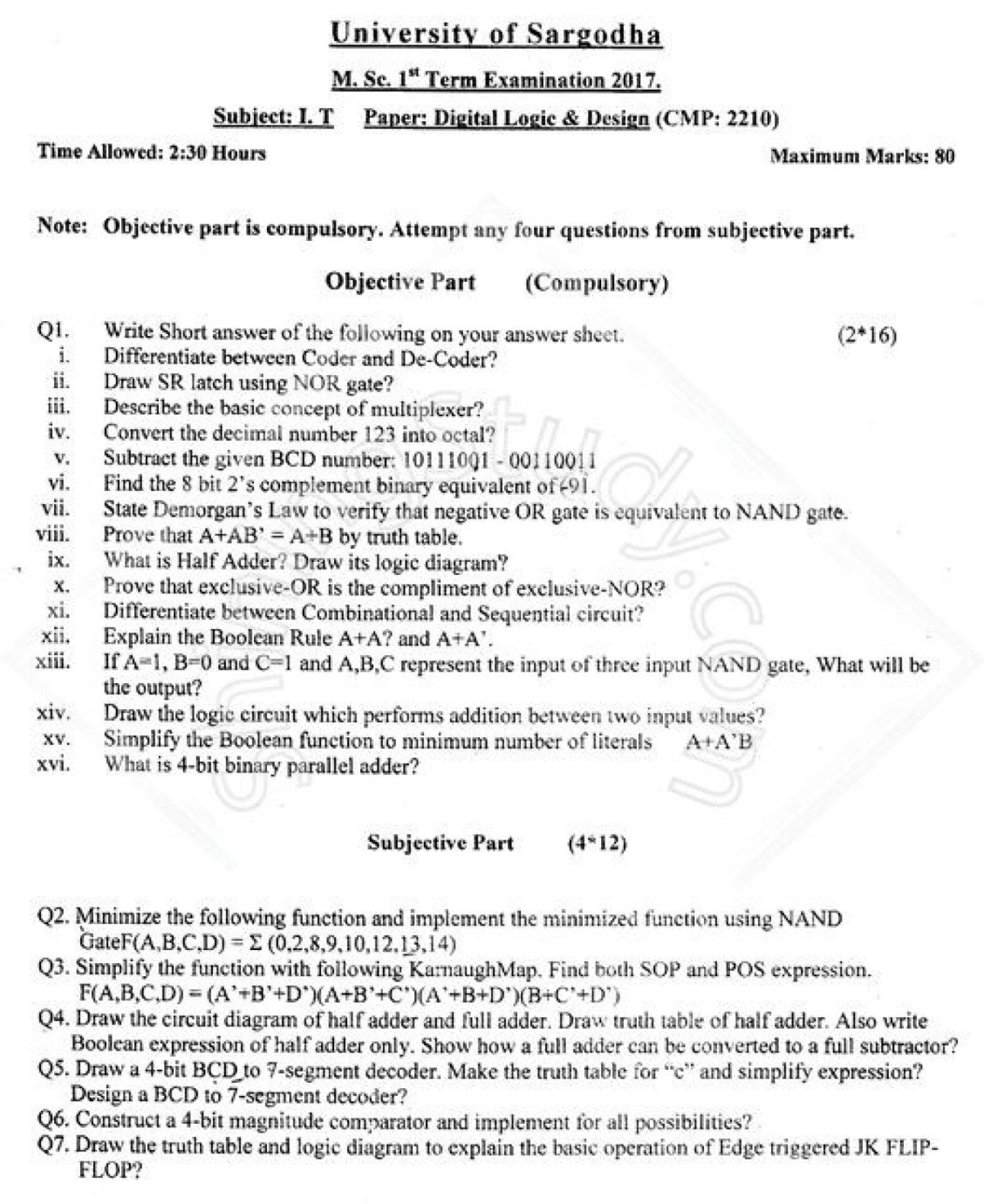

University of Sargodha

M. Sc. 1st Term Examination 2017

Subject: I.T

Paper: Digital Logic & Design (CMP: 2210)

Time Allowed: 2:30 Hours

Maximum Marks: 80

Objective Part (Compulsory)

Q1. Write short answers to the following on your answer sheet. (2*16)

i. Differentiate between Coder and De-Coder?

ii. Draw SR latch using NOR gate?

iii. Describe the basic concept of multiplexer?

iv. Convert the decimal number 123 into octal?

v. Subtract the given BCD number: 10111001 – 00110001

vi. Find the 8-bit 2’s complement binary equivalent of Q1.

vii. State DeMorgan’s Law to verify that negative OR gate is equivalent to NAND gate.

viii. Prove that A + AB’ = A + B by truth table.

ix. What is Half Adder? Draw its logic diagram?

x. Prove that exclusive-OR is the compliment of exclusive-NOR?

xi. Differentiate between Combinational and Sequential circuit?

xii. Explain the Boolean Rule A + A’ and A + A’.

xiii. If A=1, B=0 and C=1 and A, B, C represent the input of three input NAND gate, what will be the output?

xiv. Draw the logic circuit which performs addition between two input values?

xv. Simplify the Boolean function to minimum number of literals A + AB’

xvi. What is a 4-bit binary parallel adder?

Subjective Part (4*12)

Q2. Minimize the following function and implement the minimized function using NAND Gate:

F(A,B,C,D) = Σ(0,2,8,9,10,12,13,14)

Q3. Simplify the function with following Karnaugh Map. Find both SOP and POS expression:

F(A,B,C,D) = (A’+B+D)(A+B’C’)(B+C+D’)

Q4. Draw the circuit diagram of half adder and full adder. Draw truth table of half adder. Also write Boolean expression of half adder only. Show how a full adder can be converted to a full subtractor?

Q5. Draw a 4-bit BCD to 7-segment decoder. Make the truth table for “c” and simplify expression?

Q6. Construct a 4-bit magnitude comparator and implement for all possibilities?

Q7. Draw the truth table and logic diagram to explain the basic operation of Edge triggered JK FLIP-FLOP?