Blog

Digital Logic Design BS IT 2nd Term Past paper 2016 UOS

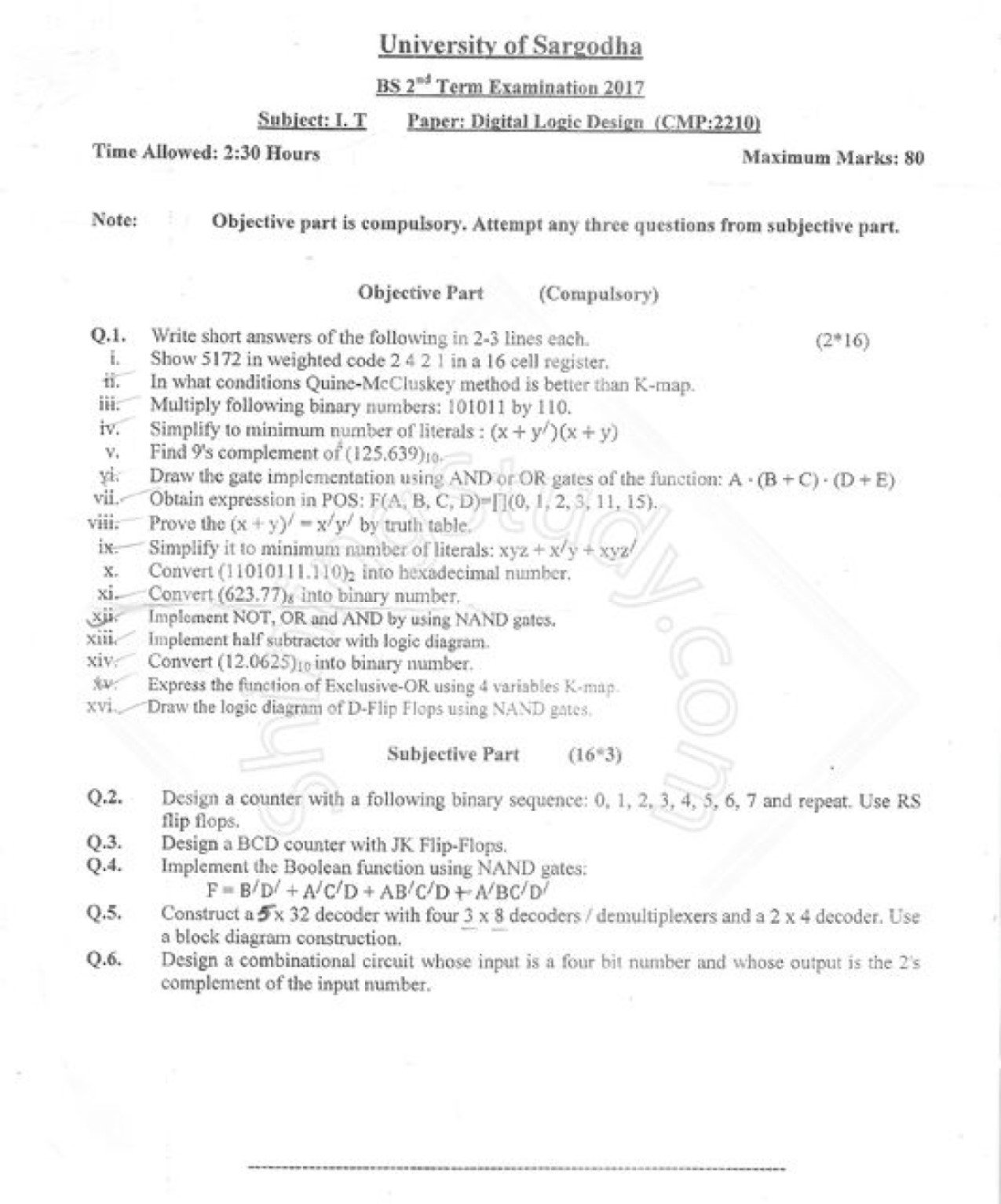

University of Sargodha

BS 2nd Term Examination 2017

- Subject: I. T

- Paper: Digital Logic Design (CMP:2210)

- Time Allowed: 2:30 Hours

- Maximum Marks: 80

Objective Part (Compulsory)

Q1. Write short answers of the following in 2-3 lines each. (2*16)

- Show 5172 in weighted code 2421 in a 16 cell register.

- In what conditions Quine-McCluskey method is better than K-map.

- Multiply following binary numbers: 101101 by 110.

- Simplify to minimum number of literals: .

- Find 9’s complement of 125.639.

- Draw the gate implementation using AND or OR gates of the function: .

- Obtain expression in POS: .

- Prove the by truth table.

- Simplify it to minimum number of literals: .

- Convert into hexadecimal number.

- Convert into binary number.

- Implement NOT, OR and AND by using NAND gates.

- Implement half subtractor with logic diagram.

- Convert into binary number.

- Express the function of Exclusive-OR using 4 variables K-map.

- Draw the logic diagram of D-Flip Flops using NAND gates.

Subjective Part (16*3)

Q2. Design a counter with the following binary sequence: 0, 1, 2, 3, 4, 5, 6, 7 and repeat. Use RS flip flops.

Q3. Design a BCD counter with JK Flip-Flops.

Q4. Implement the Boolean function using NAND gates:

Q5. Construct a 5×32 decoder with four 3×8 decoders / demultiplexers and a 2×4 decoder. Use a block diagram construction.

Q6. Design a combinational circuit whose input is a four bit number and whose output is the 2’s complement of the input number.